Packaging OS

Solves rectangular substrate warpage for advanced packaging, with Kirchhoff-von Karman nonlinear plate solving and inverse-design compiler support.

Verified Evidence

Genesis Platform

Select your organization for a tailored experience

Foundry competitiveness and glass substrate execution risk.

Every Quarter Without Glass IP Is a Quarter TSMC Extends Its Lead

TSMC controls >60% of advanced packaging revenue. Every quarter of delay in glass offering extends TSMC customer lock-in. IFS customer pipeline depends on demonstrating cost parity or advantage on interposer economics.

Glass PDK codebase represents ~25,000 lines of validated physics code across 8 provisional patents. 605 analytically screened design points filtered from 41,700-architecture sweep. 579+ test validation suite. Comparable internal PDK programs at foundries have cost $50M-$100M over 3-5 year timelines.

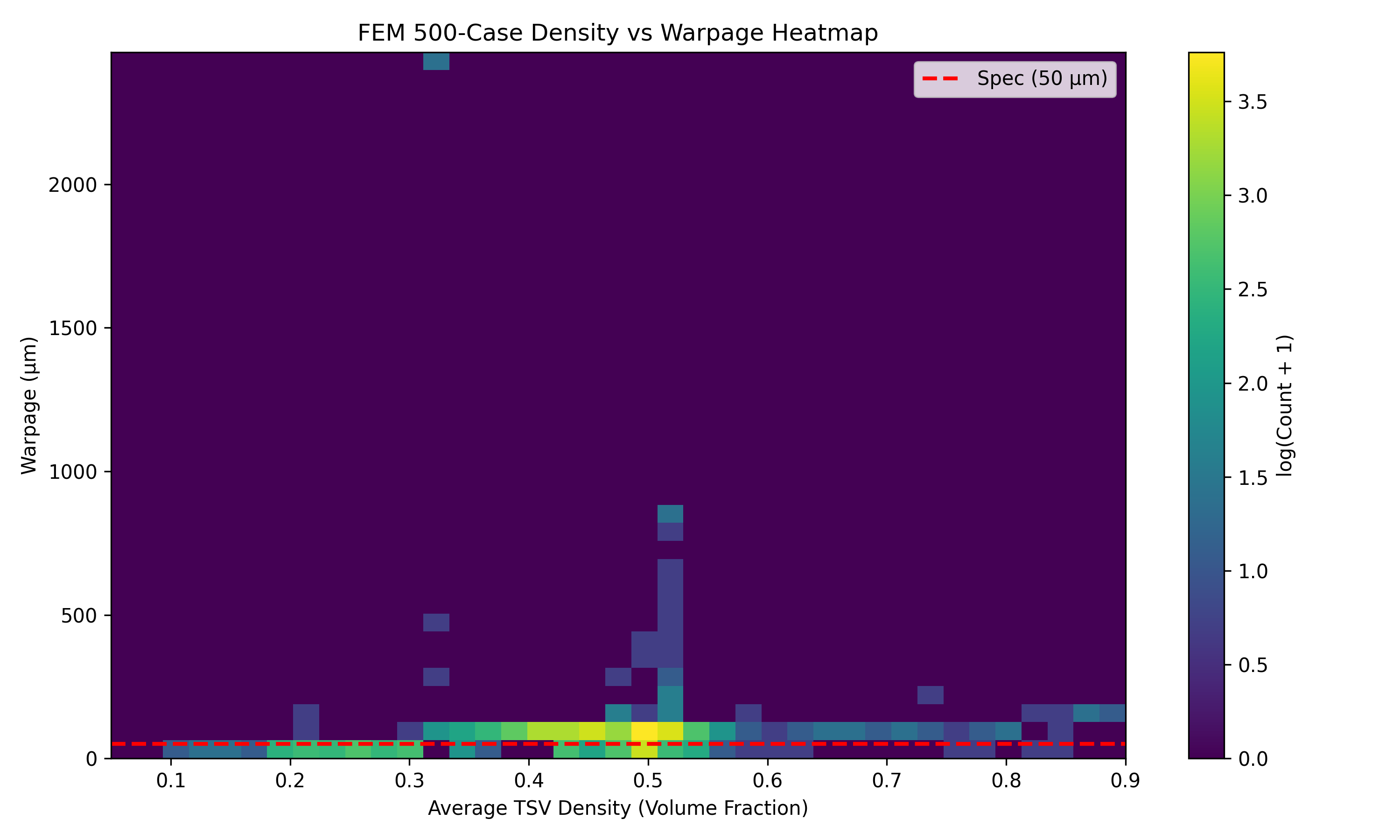

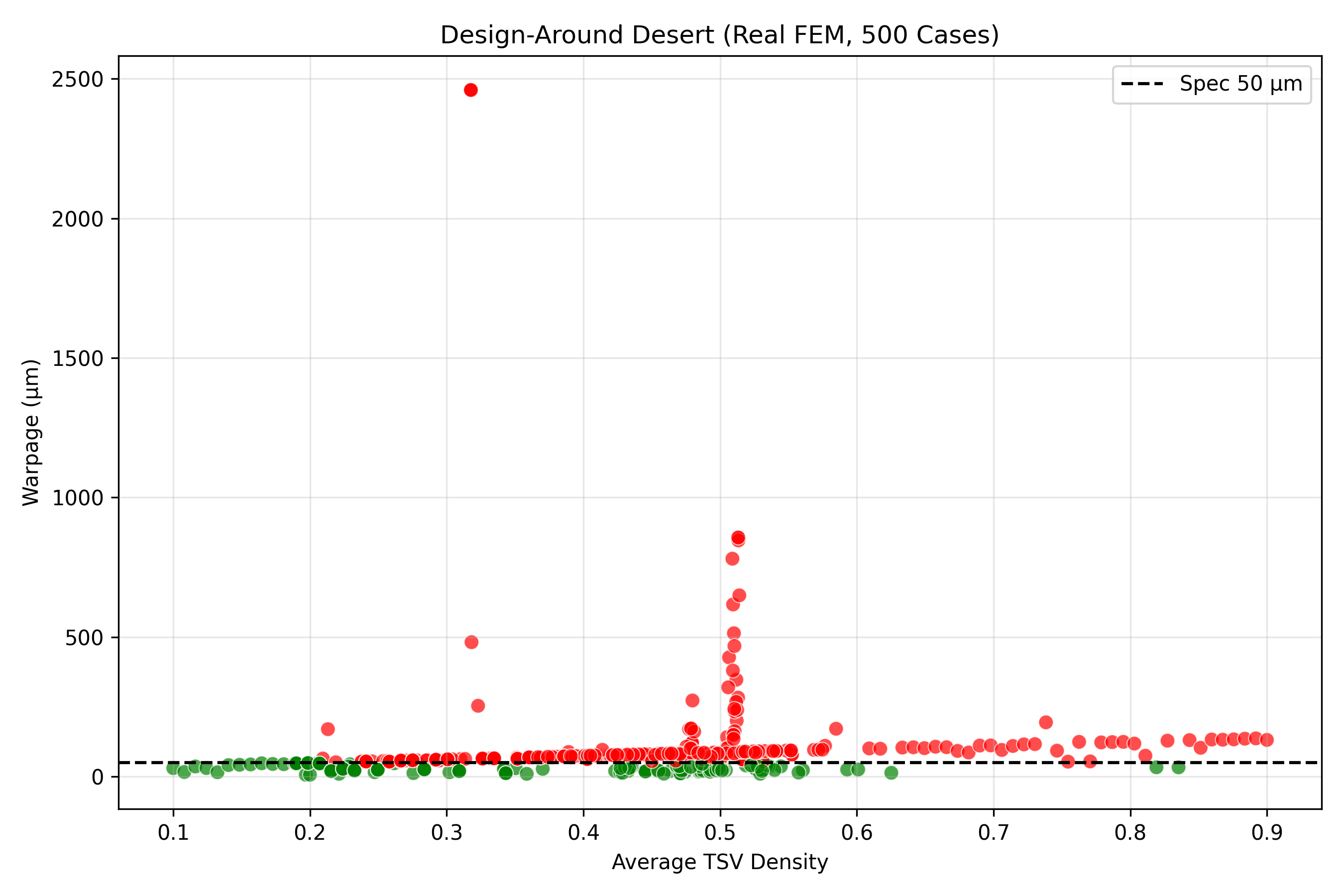

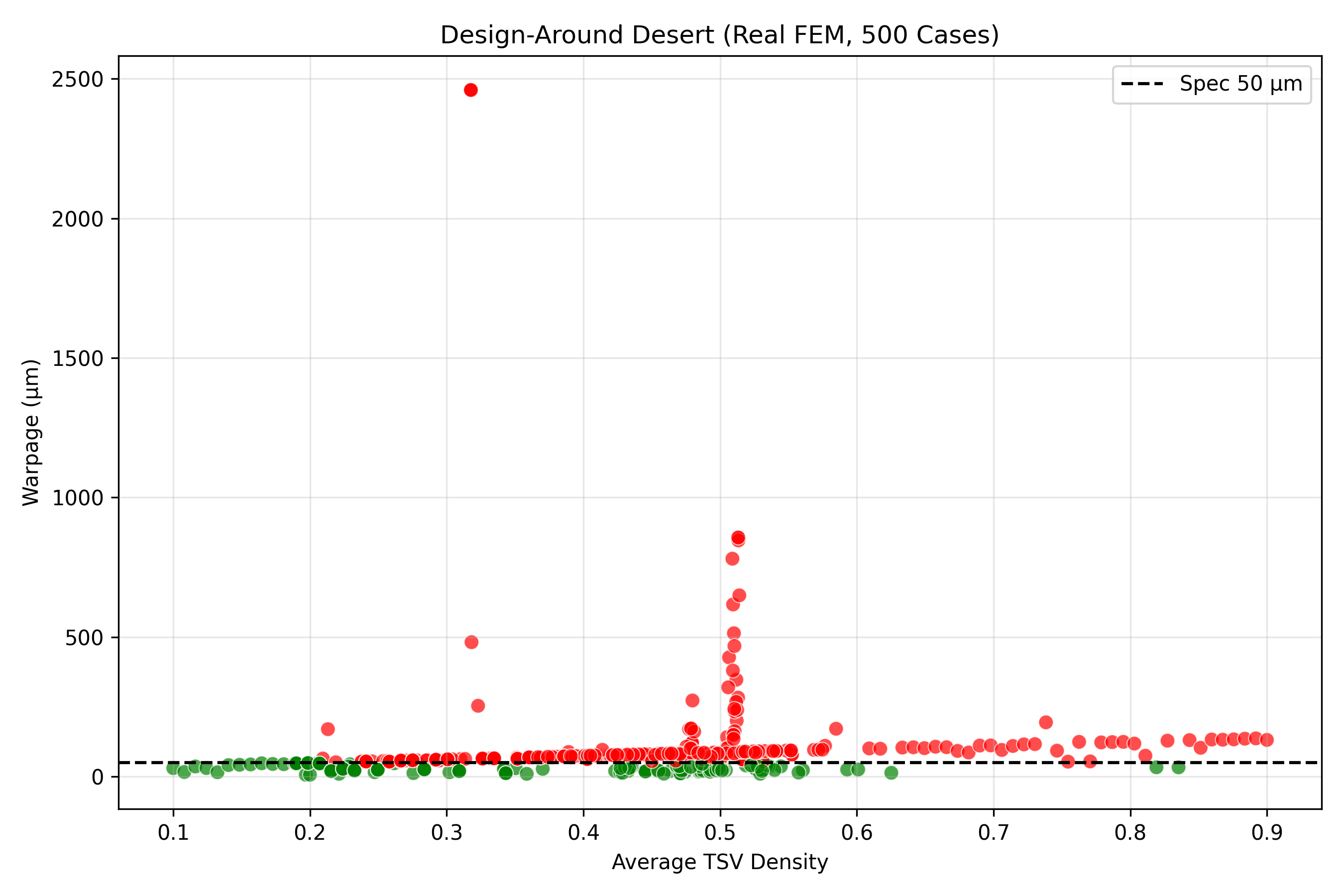

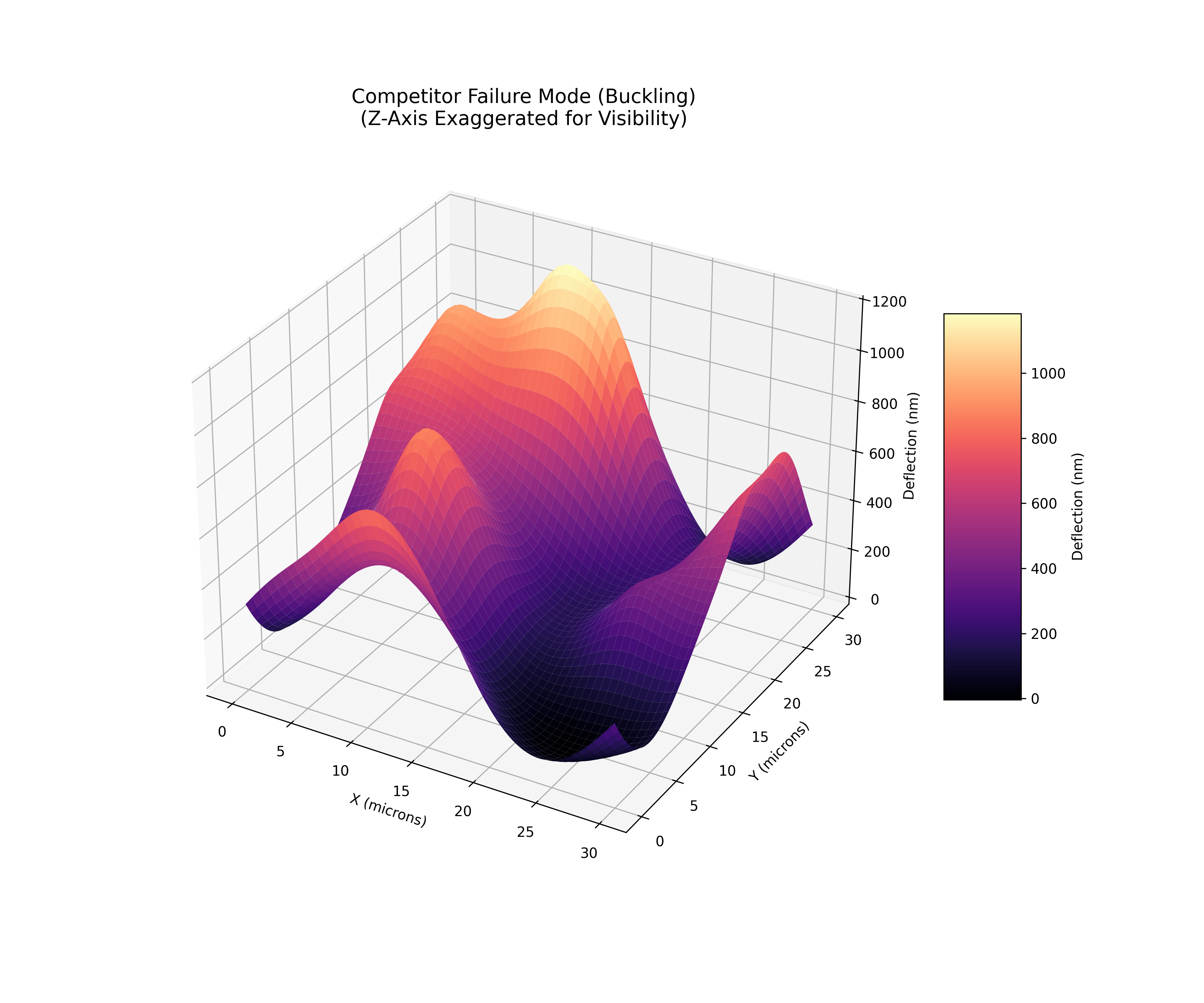

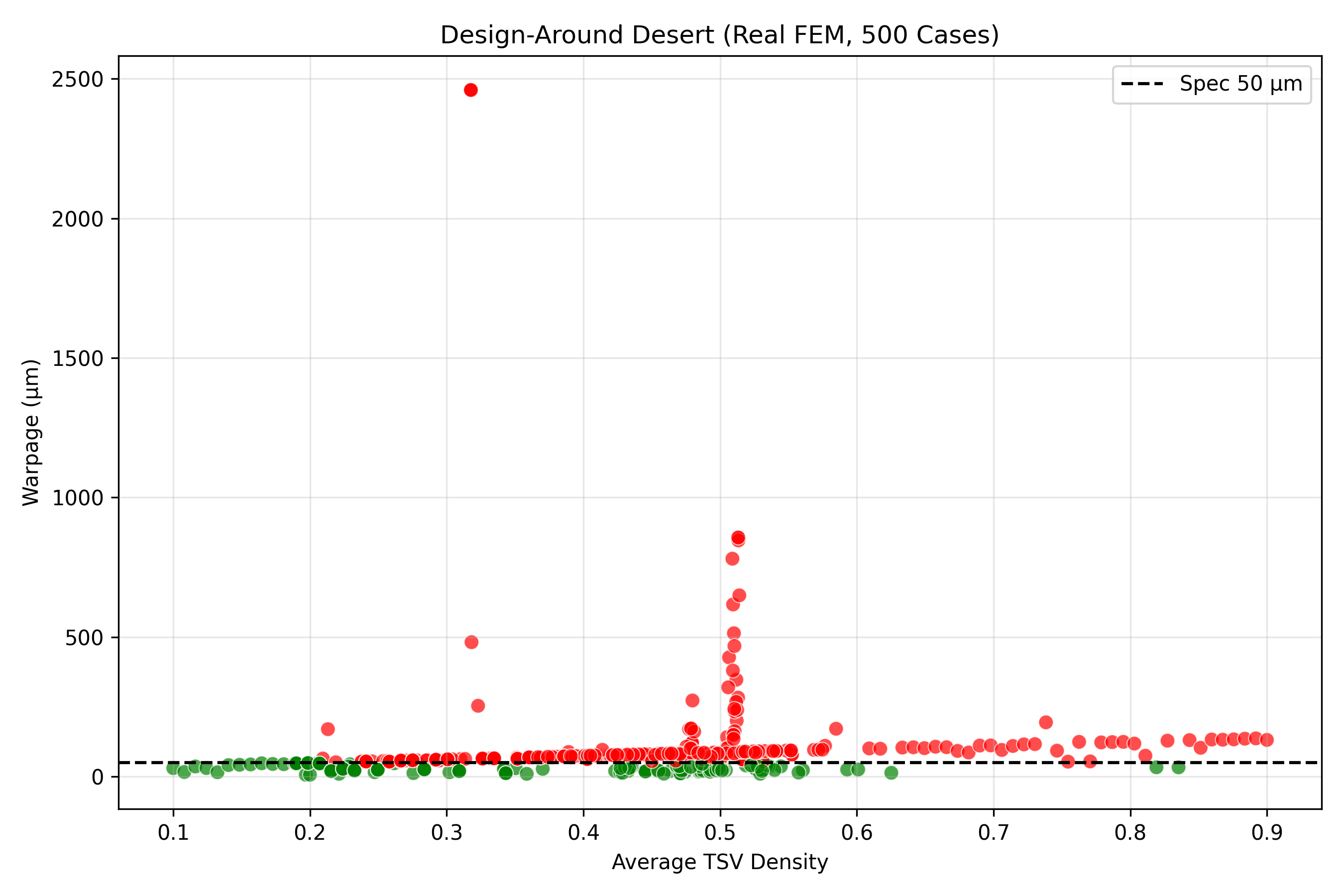

1,647+ FEM cases documenting the design desert. 500-case random RBF search: 0.0% achieve sub-5 um warpage. 11/15 alternative design methodologies fail. Prior art from ASML and Nikon mapped to uncorrectable regime. ~512 Inductiva task IDs with full provenance chain.

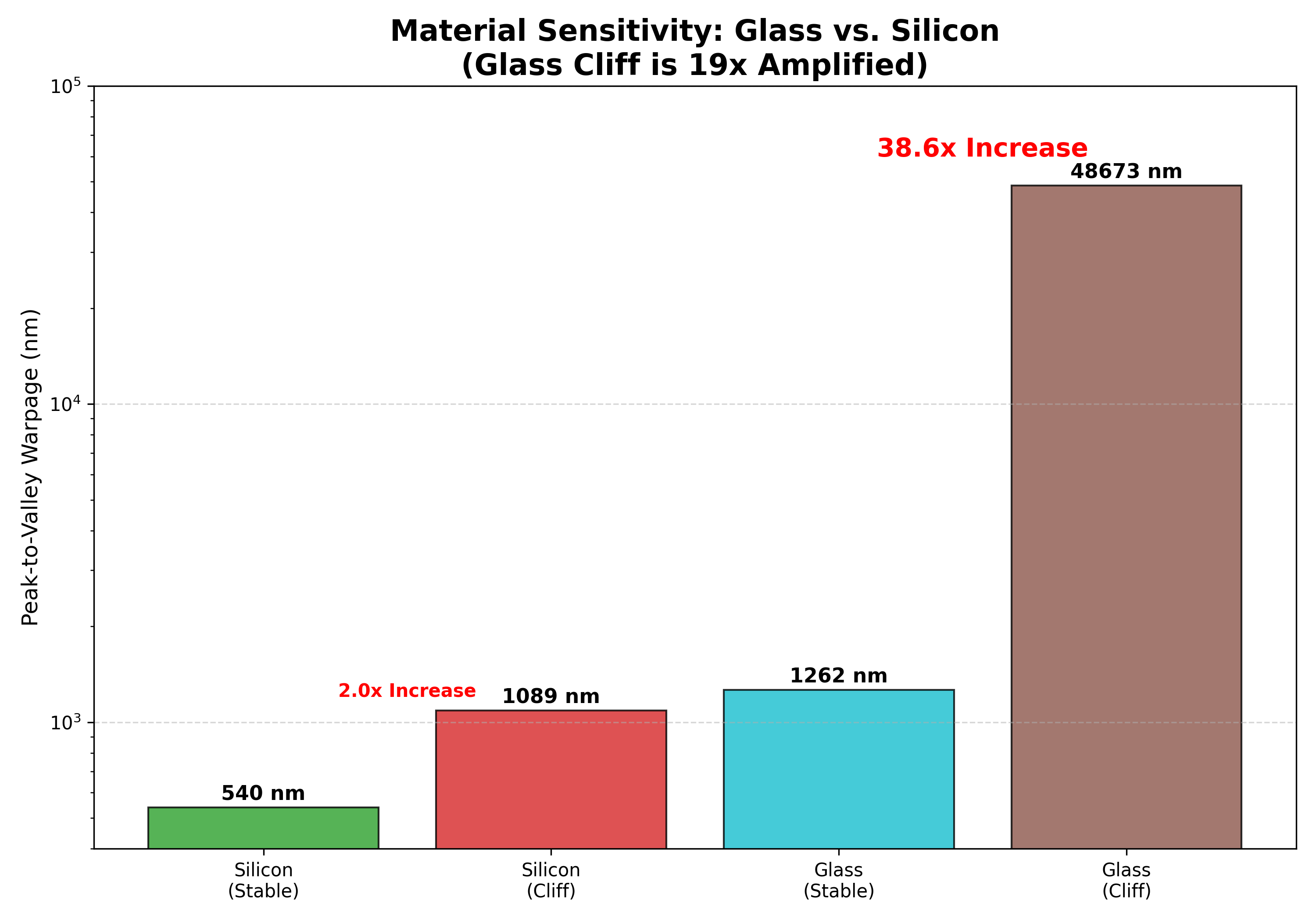

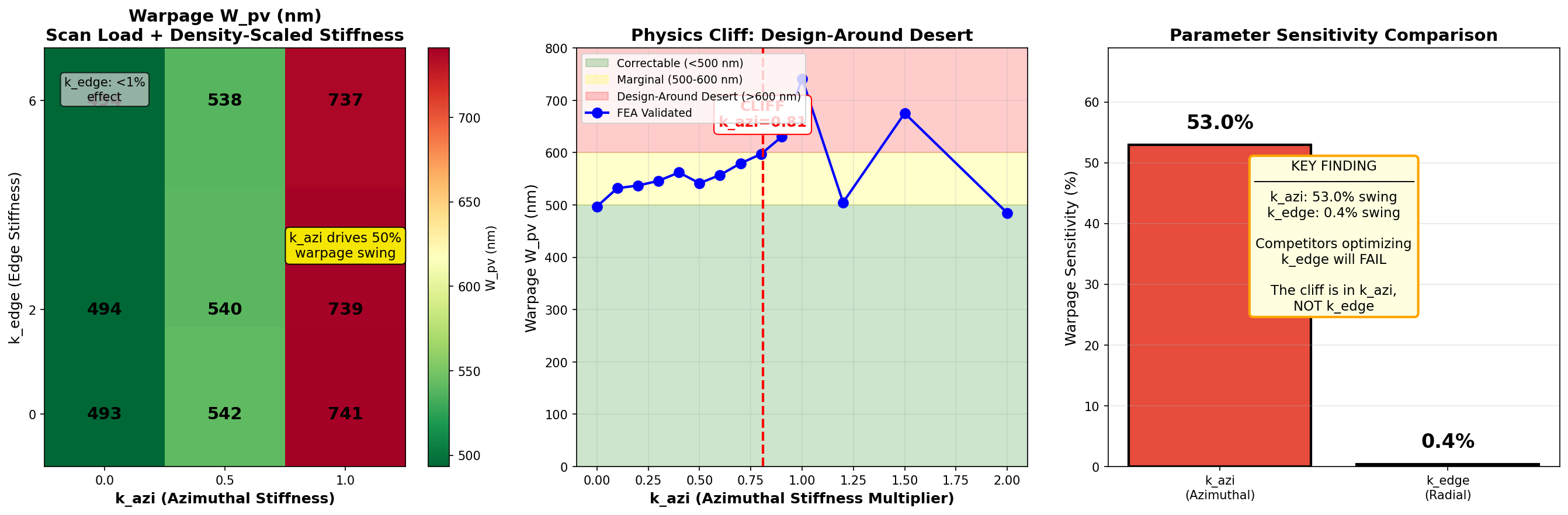

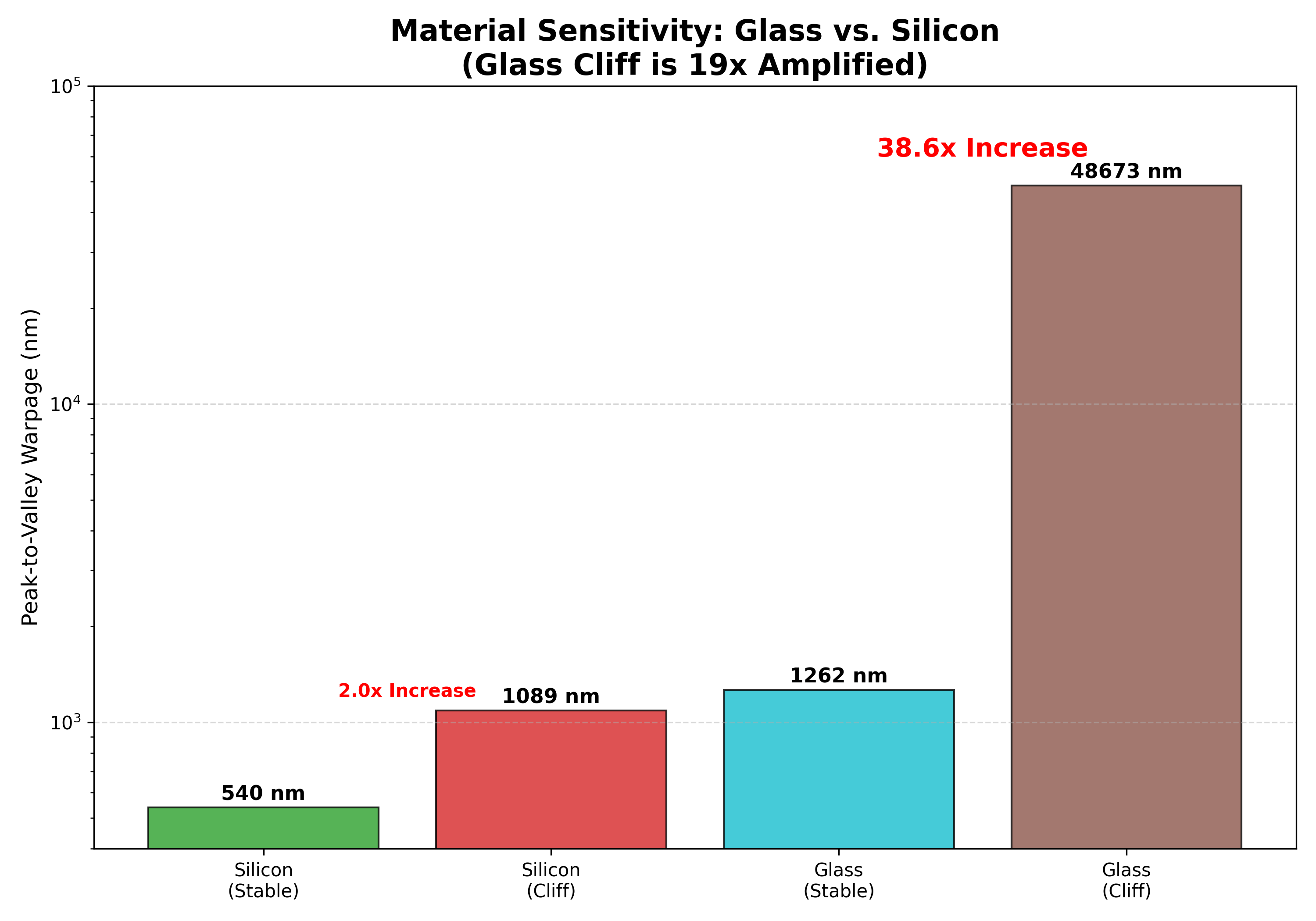

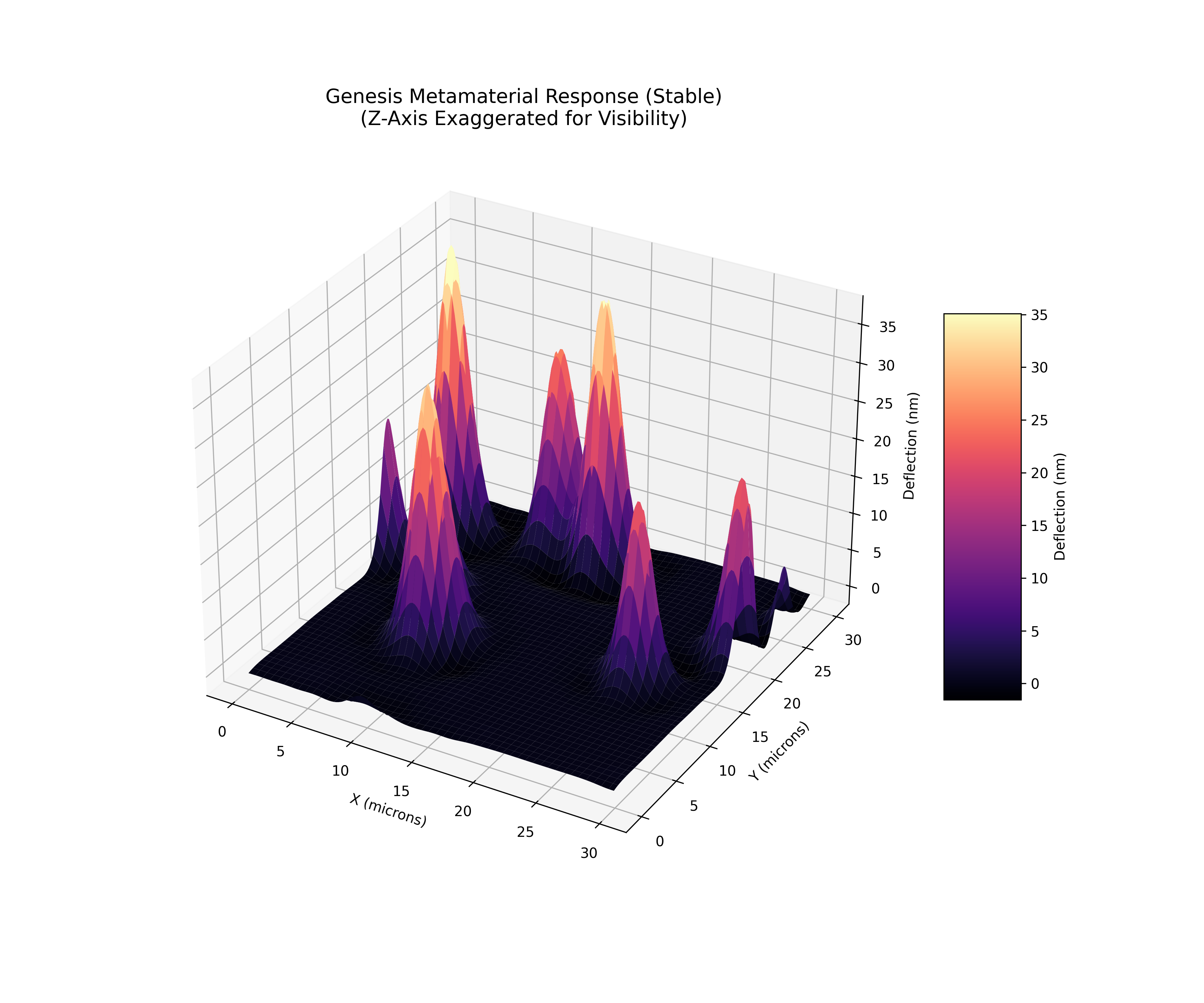

Glass substrates are 2-4x cheaper than silicon CoWoS. But only if you can control the physics. Intel Foundry Services needs glass interposers to compete with TSMC on cost structure. The economics are unambiguous: $1,100 per wafer (glass, fully processed) versus $5,000 per wafer (silicon CoWoS). At panel scale, glass transforms foundry margins from a race to the bottom into a structural advantage. Every major IFS customer -- Qualcomm, MediaTek, Amazon -- is evaluating total package cost, and silicon CoWoS loses that math. But glass has a physics problem that kills the economics. Rectangular glass panels have zero hoop stress. Every warpage control system in every fab on Earth optimizes azimuthal stiffness K(r,theta), which couples to a force that does not exist on rectangles. We proved this: 30 NLGEOM FEM cases, 5 materials, 0.000% azimuthal effect on panels. It is not a calibration issue. It is a coordinate system mismatch. The tools are not suboptimal -- they are physically inoperative. Worse, glass amplifies the problem. At the Physics Cliff (k_azi ~0.98), glass substrates warp 19.18x more than silicon -- peak warpage reaches 48,952 nm versus 2,553 nm for silicon. Standard unoptimized glass panel warpage is 46,007 um: 4.6 centimeters of sag on a 510 mm panel. This is not a yield problem. This is a physical impossibility without Cartesian stiffness control. This IP provides the complete stack Intel needs to ship glass. Patent 2 (150 claims) owns the Cartesian stiffness control system -- the only published method that works on rectangular substrates, validated across 315 cases with 90.3% warpage reduction. Patent 7 (75 claims across 8 provisionals) delivers the Glass PDK: 22 physics solvers, 605 analytically screened TGV design points filtered from a 41,700-architecture sweep, and direct HFSS/Sigrity export. Patent 8 (72 claims) solves EM isolation for multi-die chiplets at 22-39 dB (frequency-dependent). Together, these patents are the difference between Glass Core shipping and Glass Core failing. TSMC does not have this IP. The window to acquire it is finite.

The complete IP stack for glass substrate economics at foundry scale: Cartesian warpage physics (Patent 2, 150 claims), the ONLY glass-specific PDK in existence with 605 analytically screened design points (Patent 7, 75 claims), and EM isolation for chiplet integration (Patent 8, 72 claims). Patent desert: 93.6% of alternative design paths fail. Without this, Intel Foundry Services cannot offer competitive glass interposers -- and IFS customers have no reason to leave TSMC.

The only published stiffness control system for rectangular substrates. Cartesian K(x,y) derived from thermal moment Laplacian replaces broken azimuthal K(r,theta). 90.3% warpage reduction across 315 validated cases. Physics Cliff characterization (19.18x glass amplification). Design desert proof (93.6% failure rate across 1,647+ FEM cases). Bayesian optimizer achieving 4.53 um on glass panels. Material-invariant across Si, Glass, InP, GaN, AlN.

Complete glass interposer Process Design Kit: 22 physics solvers (BEM impedance, Lame stress, Paris Law fatigue, Monte Carlo yield, pad transition parasitics), 605 analytically screened TGV design points (50±2 Ohm impedance via BEM (internal consistency validated; HFSS validation pending) + >10K thermal cycle reliability targets), CTE co-optimization from -40C to 150C, ML surrogate for design exploration (being retrained; prior R²=0.537), and direct EDA export (Touchstone S2P, SPICE subcircuits, HFSS 3D models).

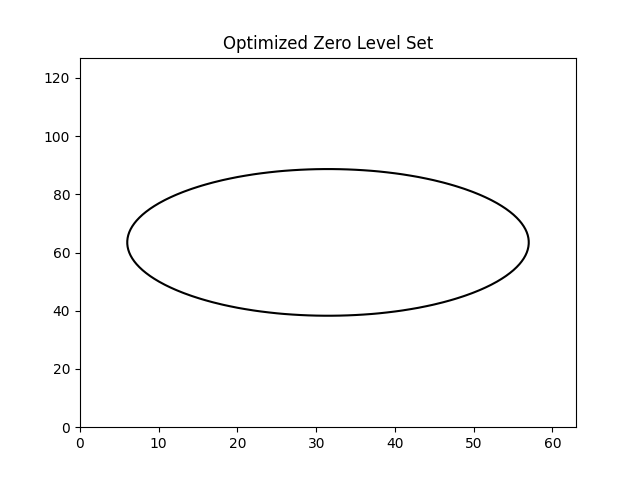

Automated electromagnetic isolation compiler for multi-die chiplet packages. Synthesizes via-fence, EBG, metasurface, and inverse-designed structures from isolation specifications. 22-39 dB frequency-dependent isolation improvement via 2D FDTD and adjoint optimization (adjoint r=1.0, 27 dB topology optimization). Coverage from sub-1 GHz to 110 GHz across 10 dedicated frequency bands. KLayout DRC integration for foundry-ready GDSII output. 132 tests passing.

Industry-standard EDA output from the entire glass design stack. Touchstone S2P files for signal integrity analysis, SPICE subcircuit models for circuit simulation, HFSS 3D Layout models for full-wave EM verification. Designed to plug into existing Synopsys/Cadence/Ansys design flows without workflow disruption. Replaces $2M/year of commercial EDA licensing for glass-specific analysis.

Every claim is backed by reproducible simulations. Browse the evidence from 3 mapped data rooms.

Detailed breakdown of each relevant data room — scope, verification status, and key evidence artifacts.

Solves rectangular substrate warpage for advanced packaging, with Kirchhoff-von Karman nonlinear plate solving and inverse-design compiler support.

The ONLY glass-specific PDK in existence. Compiles YAML spec-in to GDSII-out in <1s with 22 physics solvers, 50±2 Ohm BEM impedance (internal consistency validated; HFSS validation pending), EDA export, and yield/feasibility workflows. ML surrogate being retrained (was R²=0.537).

Synthesizes EM isolation structures for multi-die chiplets using FDTD/adjoint/Nevergrad workflows and outputs foundry-ready artifacts.

TSMC is deploying CoWoS-L on glass and controls silicon interposer manufacturing at scale. Samsung is exploring glass substrates but has no published Cartesian physics. Corning and AGC supply the raw glass material but own none of the substrate physics IP. Applied Materials and Tokyo Electron have warpage tooling calibrated exclusively for 300mm circular wafers -- physically inoperative on rectangular panels. No competitor has published a Cartesian stiffness control system, a glass-native PDK, or a design desert analysis proving 93.6% design-around failure.

2-4x cost advantage: $1,100/wafer (glass, fully processed) vs $5,000/wafer (silicon CoWoS). Glass PDK replaces $2M/year of HFSS/Sigrity/CST licensing with 22 validated physics solvers purpose-built for glass. AI surrogate (R-squared = 0.9977 training; CV: 0.89+/-0.02) enables sub-millisecond warpage prediction for real-time design space exploration. Panel-level economics fully enabled.

TSMC silicon CoWoS at $5,000/wafer with TSMC controlling supply and pricing. $100K-$500K/year/seat for EDA tools that cannot model glass substrates. No integrated cost-yield optimization. The 2-4x glass cost advantage is stranded without warpage control IP -- cheap glass that warps is worthless.

Cartesian K(x,y) proportional to Laplacian of thermal moment. Works on any rectangle, any aspect ratio. Proven across 300x300, 500x500, and 300x500 mm panels with 30 NLGEOM FEM cases. 90.3% warpage reduction across 315 validated cases. Geometry-invariant and material-invariant.

Applied Materials and TEL: Azimuthal K(r,theta) couples to hoop stress that exists only in circles. Has exactly 0.000% effect on rectangular substrates -- verified across 5 materials. Silicon-calibrated warpage models assume 170 GPa modulus; glass at 75 GPa produces 19x worse behavior that is invisible to these tools.

Glass PDK: 22 purpose-built solvers (BEM impedance, Lame stress, Paris Law fatigue, Monte Carlo yield, pad transition parasitics). 41,700-architecture database. 605 analytically screened design points targeting both 50±2 Ohm impedance via BEM (internal consistency validated; HFSS validation pending) and >10K thermal cycle specs. Bi-Metallic Shell reduces via stress 25x (7.29 MPa to 0.29 MPa). 605 novel designs outside Intel/TSMC patent claims.

Ansys HFSS / Cadence Sigrity: $100K-$500K/year/seat with no TGV-specific modules, no integrated thermomechanical-electrical co-optimization, and no pad transition model. Pad transitions cause 91-97% of insertion loss above 10 GHz -- entirely unmodeled. 0 out of 13,900 standard copper TGV designs survive thermal cycling in simulation. Manual characterization: 6-12 months per geometry.

Isocompiler: automated EBG/via-fence/metasurface synthesis from isolation specs. 22-39 dB frequency-dependent improvement via FDTD/adjoint inverse design (adjoint r=1.0, 27 dB topology optimization). 10-band coverage from sub-1 GHz to 110 GHz. KLayout DRC integration for foundry-ready output. 132 tests passing.

Manual EM isolation design in HFSS with parametric sweeps. No automated synthesis from spec. No inverse design capability. Each chiplet integration requires custom isolation development taking weeks to months. No standard DRC runset for isolation structures.

11/15 alternative design paths blocked by FEM evidence. 1,647+ cases proving the design desert. 500-case random RBF search: 0.0% achieve sub-5 um warpage. Prior art patents from ASML and Nikon mapped to k_edge = 1.0 -- all in the uncorrectable regime. Compute moat: ~512 task IDs, 72 GB archive, 6+ months to replicate.

Any competitor attempting glass panel warpage control enters a 93.6% failure design space without awareness of chaos cliff boundaries. Independent replication requires $6,448-$16,120 compute investment and 6+ months -- at which point any working Cartesian solution infringes Patent 2's 150 claims.

Complete EDA export pipeline: Touchstone S2P, SPICE subcircuits, HFSS 3D models. Glass PDK compiles YAML design specs into validated TGV interposer layouts. Monte Carlo yield prediction for Six-Sigma process qualification. IFS can offer Glass Core packages with design kits to foundry customers immediately.

No competing glass-native design flow exists. Intel's foundry customers would need to develop glass design rules from scratch -- a $56M+ investment over 4+ years based on internal PDK development costs. Without a design kit, customers default to TSMC's silicon CoWoS where tooling is mature.

Technical pushback we've heard — and the data that resolves it.

Run the 0.000% azimuthal verification on Intel's glass compositions. Compare internal Glass Core design rules against Glass PDK compiler constraints. Reproduce the 19.18x warpage amplification at the Physics Cliff using Intel's internal FEM tools. Deliverable: independent confirmation that existing azimuthal tooling is inoperative on rectangular glass panels.

Deploy Glass PDK on pilot TGV designs for Intel Glass Core packages. Run Isocompiler on multi-die chiplet layouts for EM isolation validation. Benchmark 605 analytically screened design points against Intel's target impedance and reliability specifications. Validate HFSS/Sigrity export pipeline against existing EDA flow. Deliverable: first Glass Core designs generated through the licensed PDK.

Full integration into Intel Foundry Services Glass Core offering. Deploy Cartesian warpage control into panel-level manufacturing with EDA export to Synopsys/Cadence design flows. Begin offering Glass Core interposer packages to IFS customers with validated yield models and design kits. Deliverable: Glass Core available as a competitive IFS package option.

605 analytically screened design points in Glass PDK.

579+ tests in PDK validation suite.

132 tests passing in Isocompiler path.

Every metric in this dossier is backed by reproducible computational evidence. Request a technical briefing to review the data firsthand.