Fab OS (YieldOS)

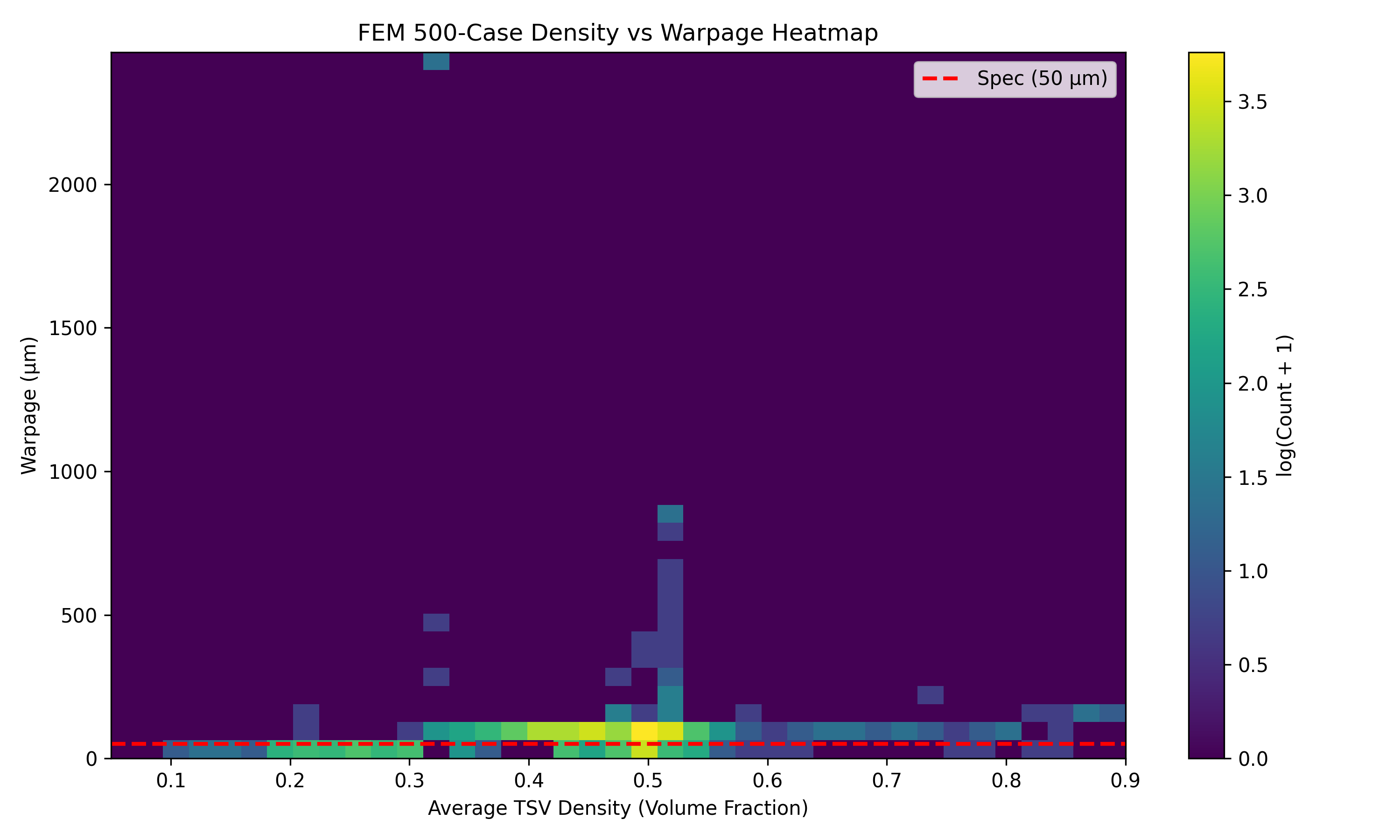

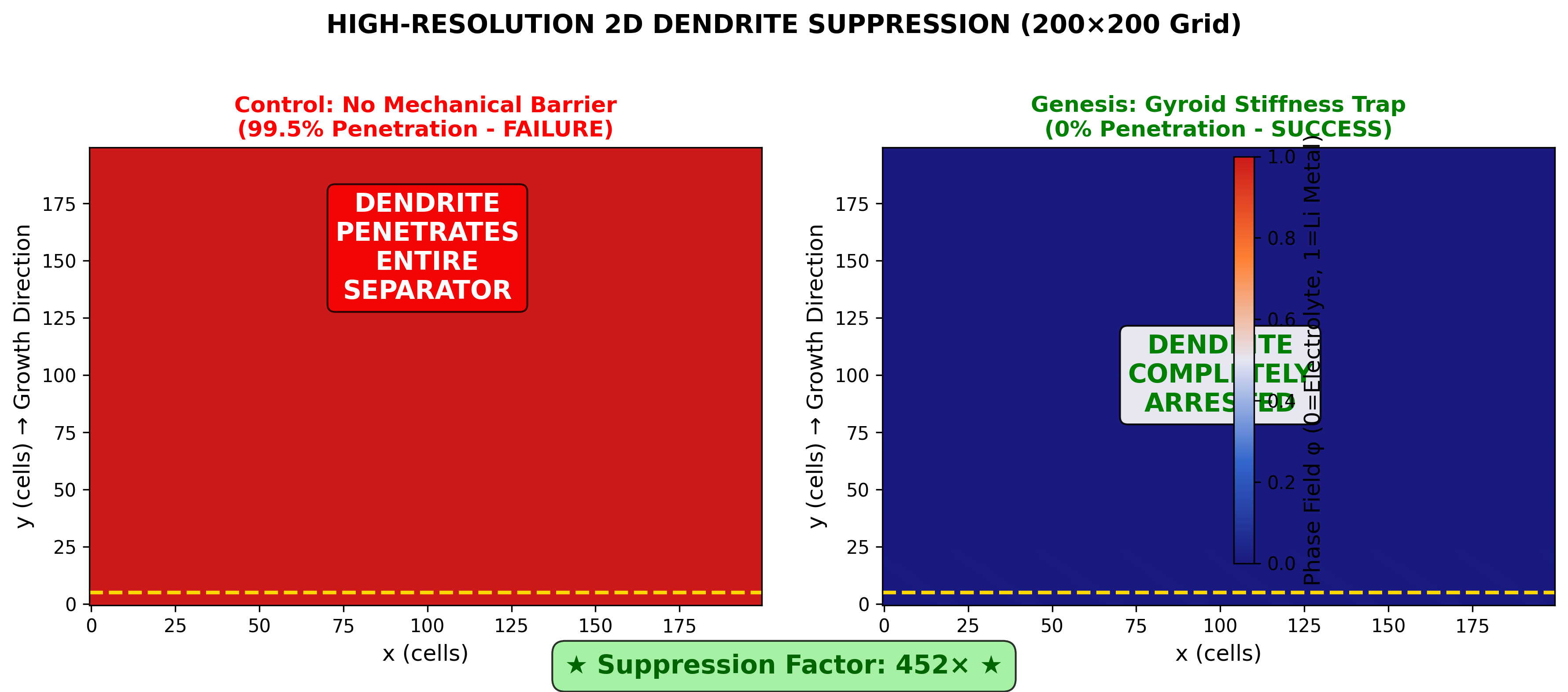

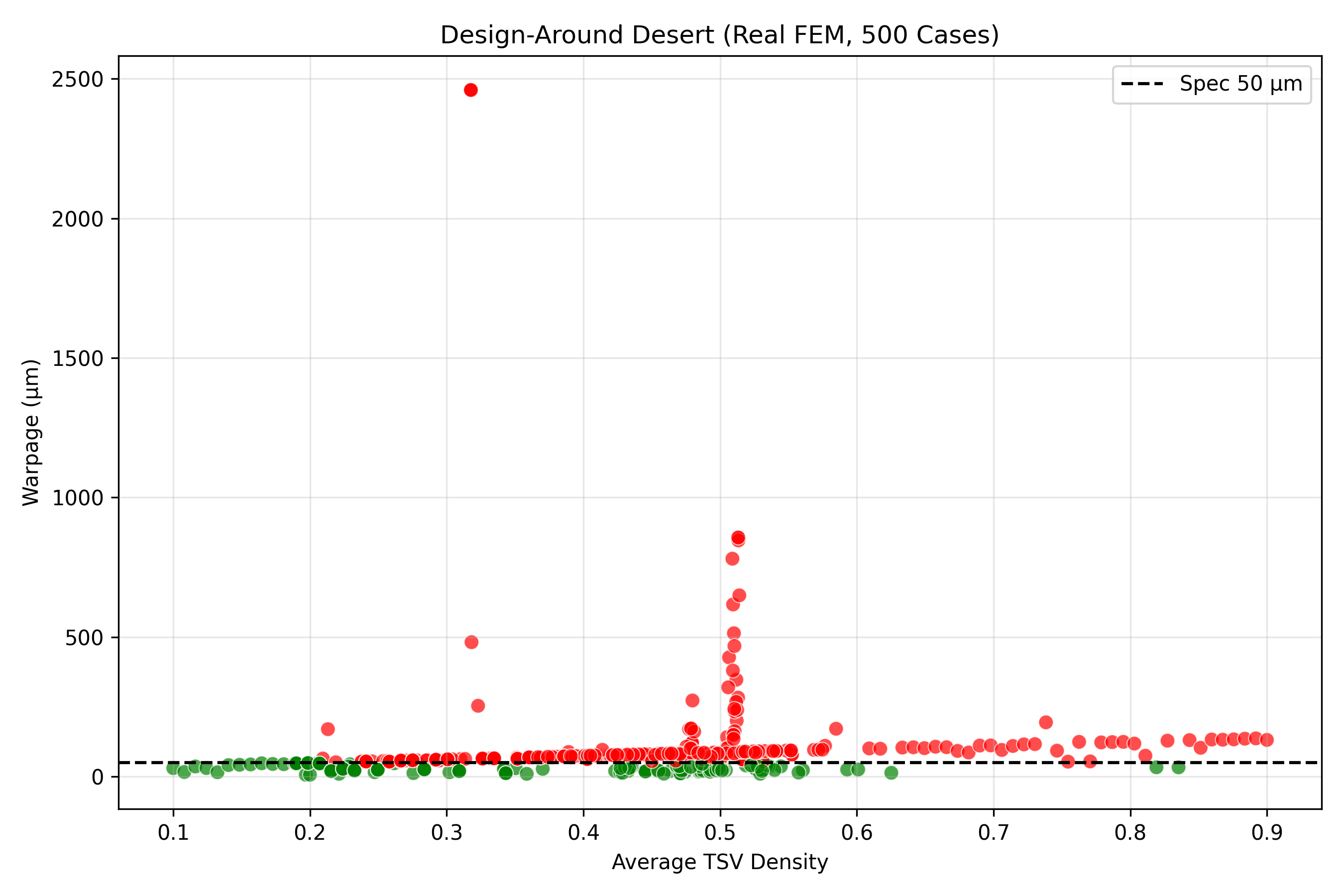

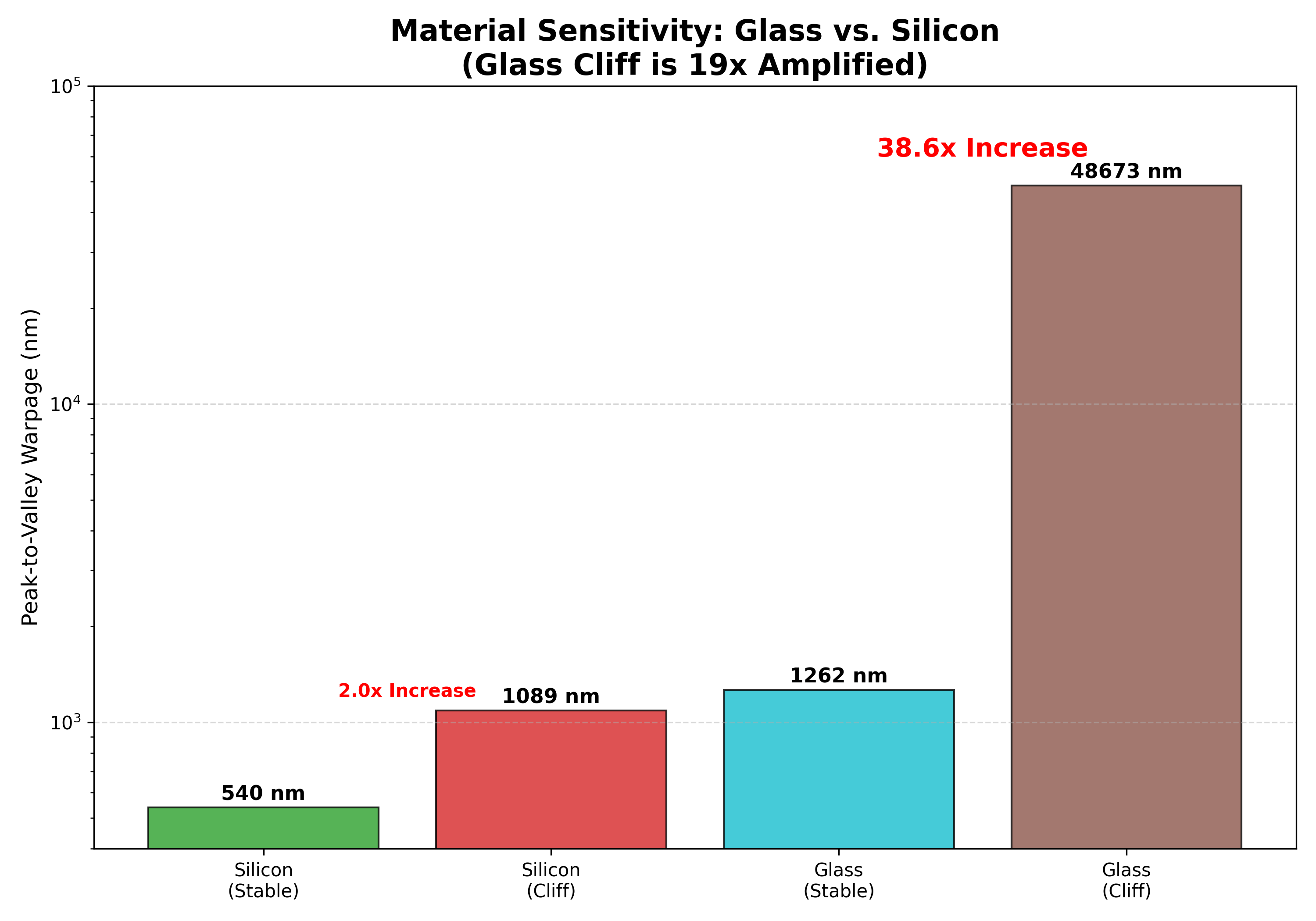

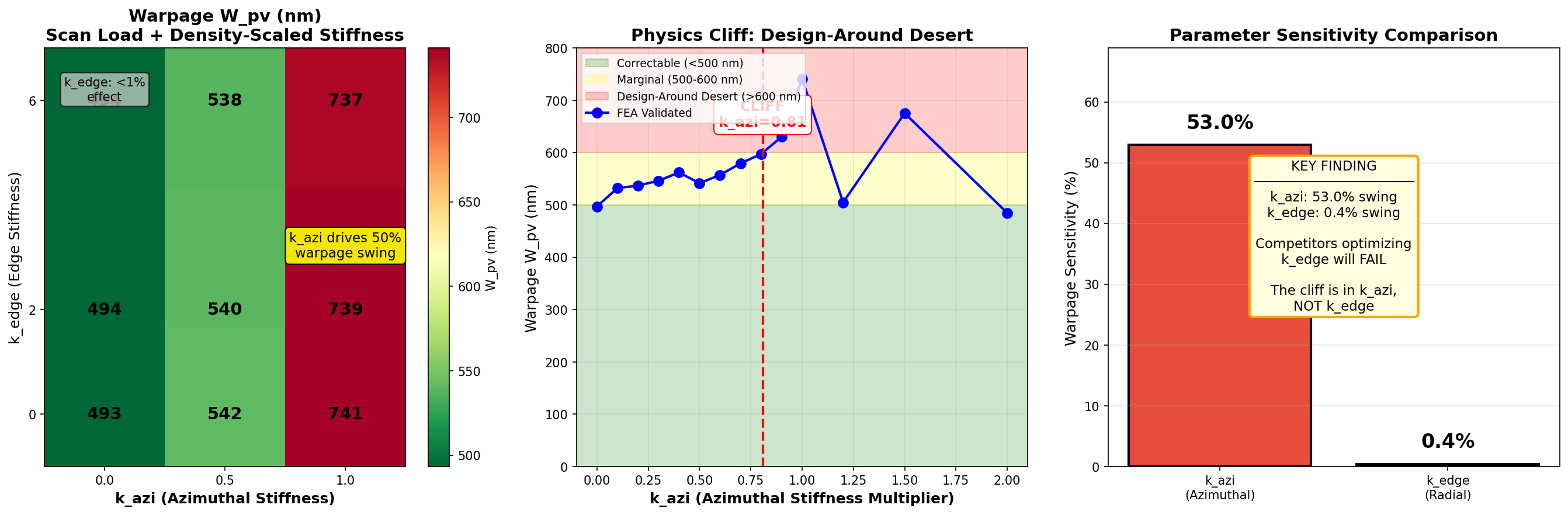

Predicts and corrects wafer warpage during High-NA EUV lithography using biharmonic FEM (0.028% error, Richardson p=1.13), iterative learning control, and ROM surrogates (R²=0.975). Physics Cliff onset k_azi=0.80, peak 2.49x silicon. 11,000 parametric FEM solves, 200 samples/point.

- PROV_1_FAB_OS/04_Source_Code/

- PROV_1_FAB_OS/05_Models/

- 11,000 parametric FEM solves, 200 samples/point

- 0.028% FEM error at N=320, Richardson p=1.13, ±0.71% bound

- 13.2x design-around gap (Genesis ILC 90.5nm vs Kitchen Sink 1198nm)

Representative evidence chart for Fab OS (YieldOS).