90.3%

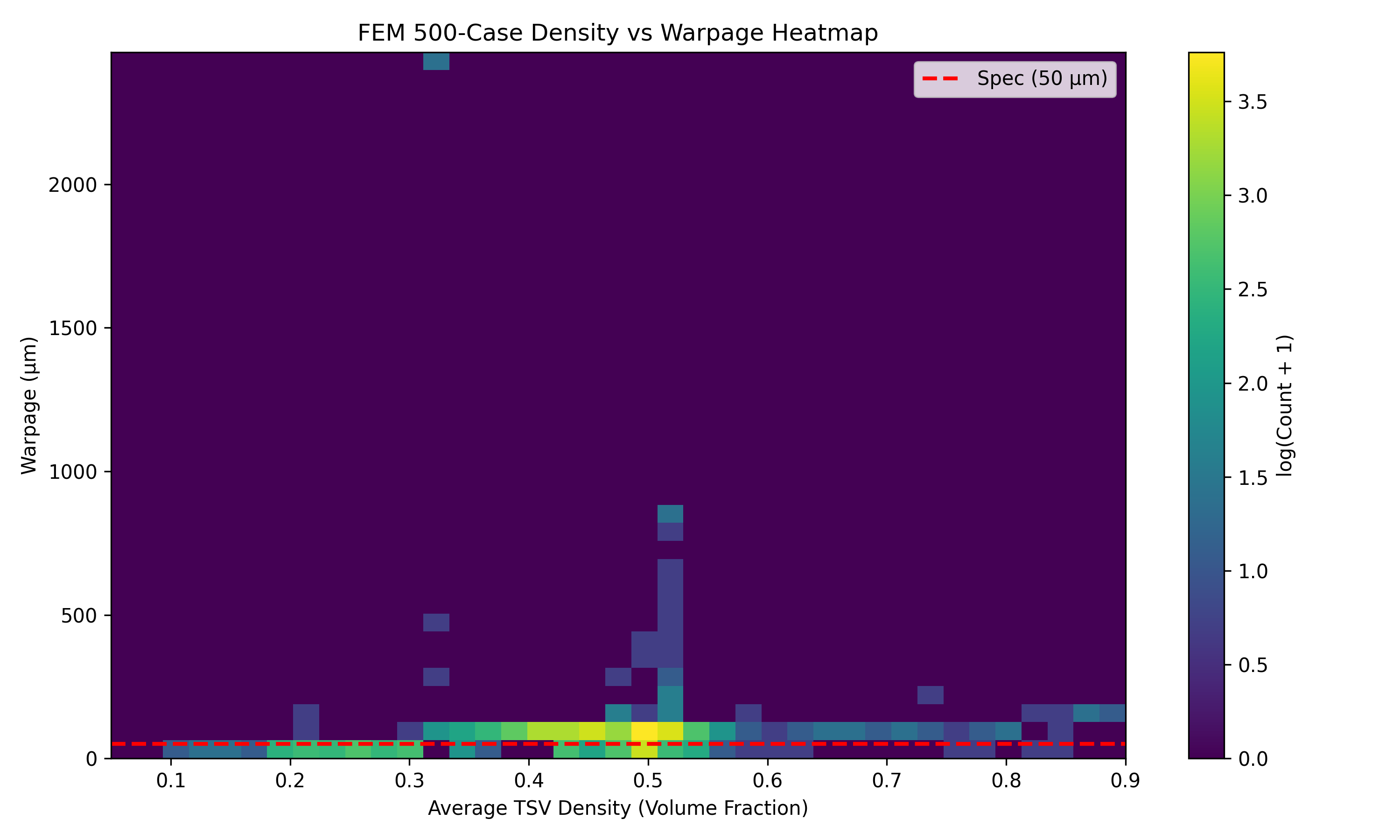

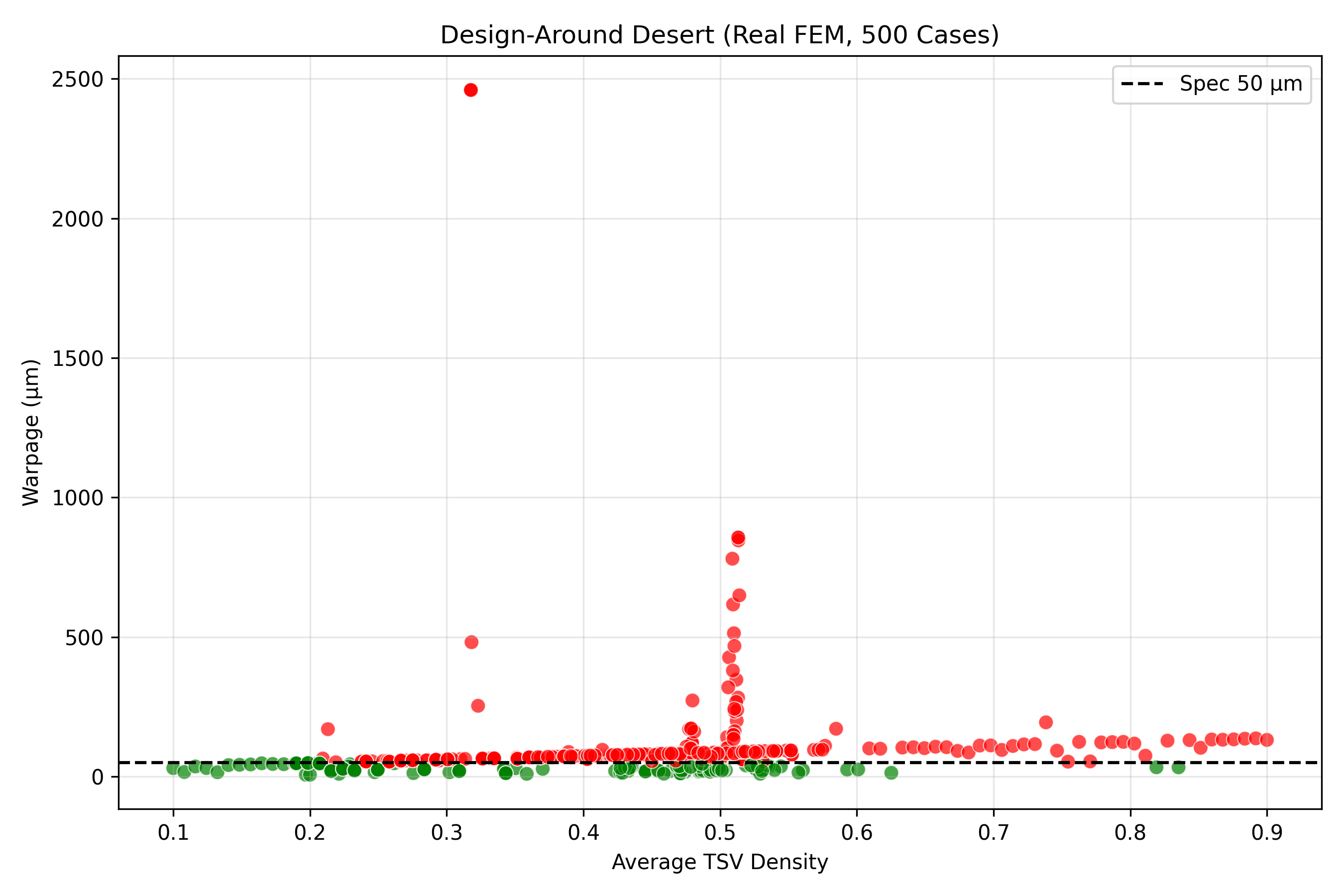

Warpage Reduction

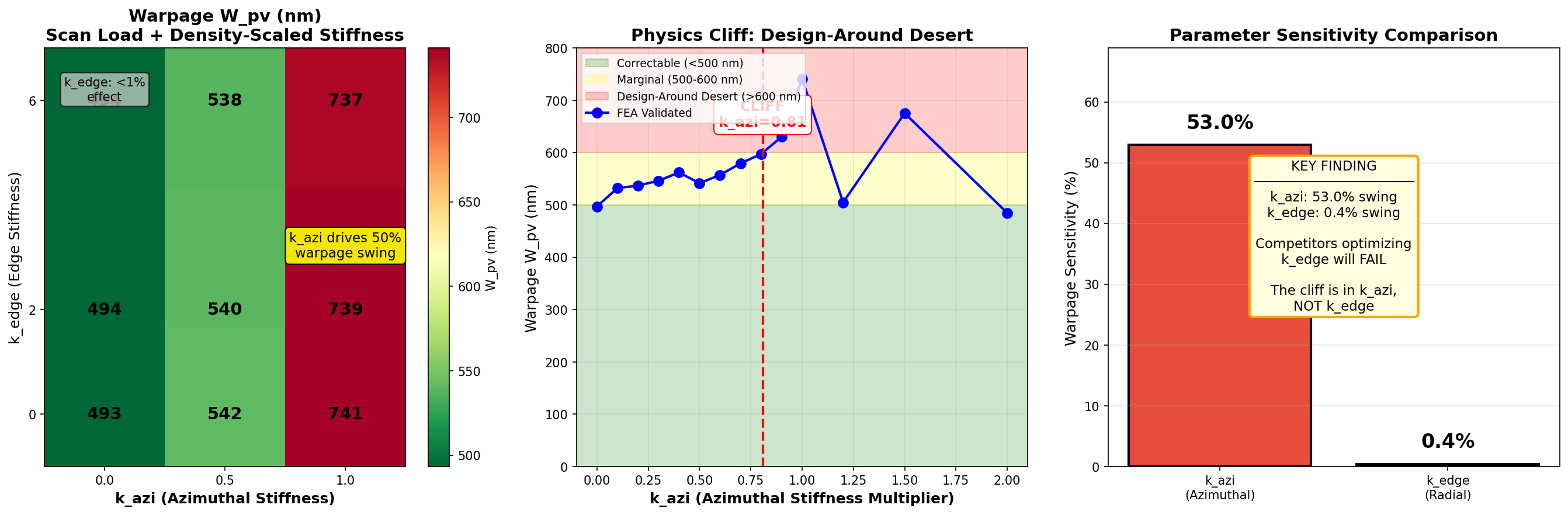

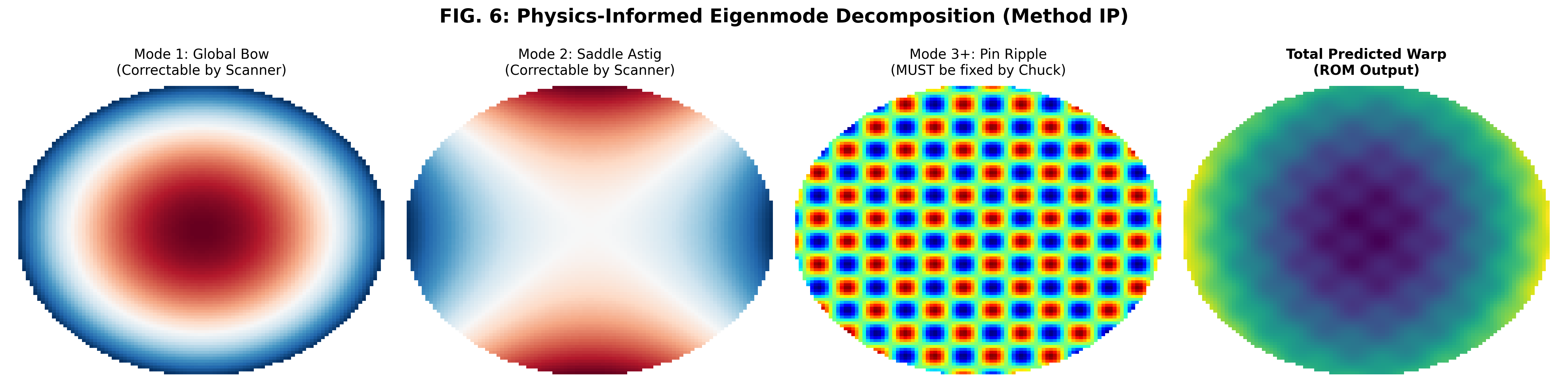

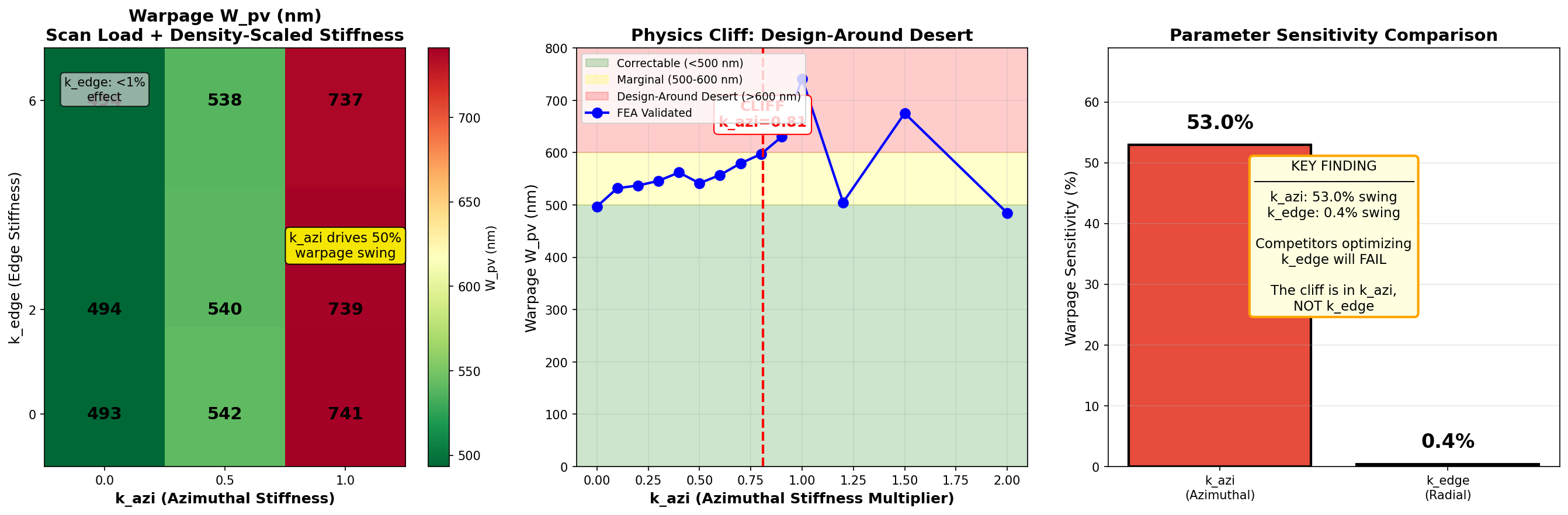

90.3% mean reduction across a 315-case validation batch (5 materials x 7 k_azi values x 3 load patterns x 3 thermal loads) — the difference between 46,000-micrometer glass panel bow and sub-5-micrometer flatness required for CoWoS-L overlay specifications. This is not a best-case cherry-pick: median reduction is 93.4%, with zero failures across the entire batch.

0.000%

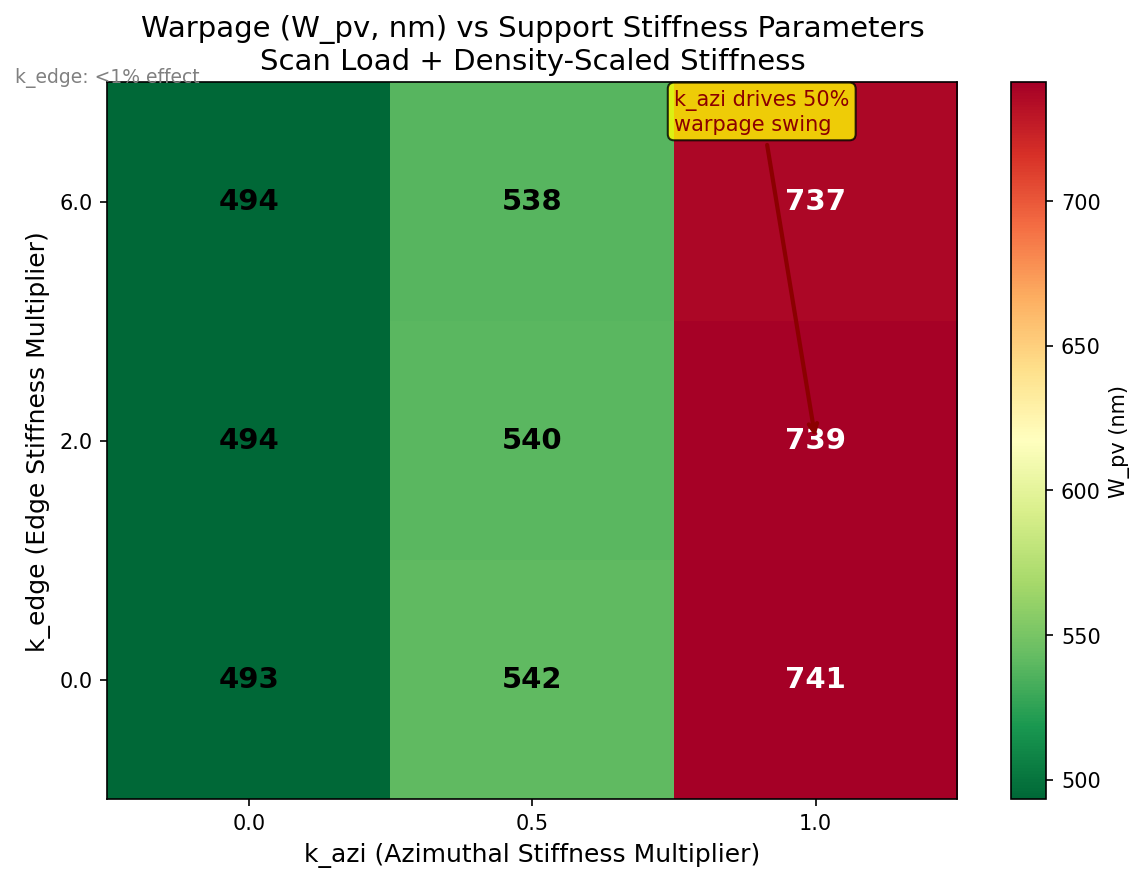

Azimuthal Effect on Panels

Azimuthal stiffness modulation — the parameter your entire wafer control stack optimizes — has exactly zero effect on rectangular substrates. Verified across 30 NLGEOM FEM cases with five different materials. This means every dollar spent tuning radial tools for panel-level packaging is wasted. The physics is not degraded on rectangles; it is absent.

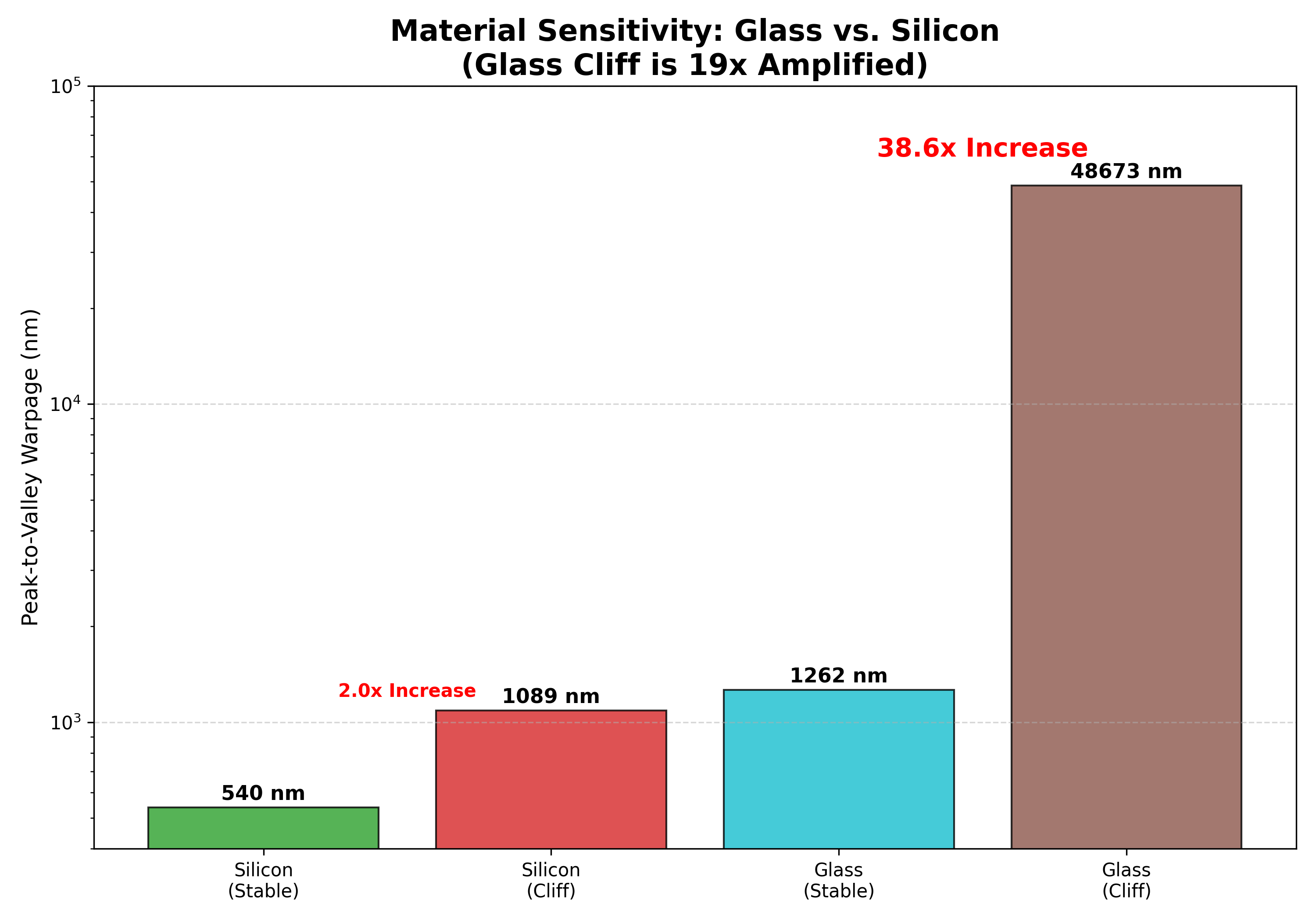

4.53 um

Best Achieved Warpage

14-run Bayesian optimization on real Inductiva cloud FEM achieved 4.53 micrometers on glass panels — within CoWoS-L overlay specification. Every evaluation is backed by a verified task ID. Your baseline without Cartesian control: 46,000 micrometers. That is a 10,000x improvement from an uncontrollable starting point to a production-viable endpoint.

262

Blocking Patent Claims

Patent 1 (Fab OS, 112 claims) covers the Physics Cliff discovery, Biharmonic FEM solver, ILC controller, and SECS/GEM interface. Patent 2 (Packaging OS, 150 claims) covers Cartesian stiffness control, process history compensation, and AI-accelerated inverse design across seven subsystems. Together: an impenetrable blocking position for anyone attempting localized stiffness modulation on non-circular substrates.